- با ثبتنام در دو دوره به صورت همزمان شامل تخفیف خواهید شد.

- 02166566140

- 02166402309

چگونه می توان یک استپ موتور (موتور پله ای) را کنترل کرد

2021-05-26

نحوه شبیه سازی منبع جریان کنترل شده با ولتاژ دو سر

2021-05-26در این مقاله به شما خواهیم گفت که چگونه می توانید ثبت شیفت در Verilog را انجام دهید و همچنین از پروسه کار آن نیز مطلع خواهید شد. نحوه ثبت شیفت در Verilog که در ادامه توضیح داده شده است، می تواند برای تست در سخت افزار واقعی با کمک FPGA ساخته و بارگیری شود.

قبل از شروع مقاله باید از شما بخواهم، در صورتیکه به دنبال یادگیری تخصصی تعمیرات برد الکترونیکی هستید حتما از سرفصل های دوره آموزش تعمیرات برد الکترونیکی فنی پویان دیدن کنید.

مفاهیم اصلی ثبت شیفت در Verilog

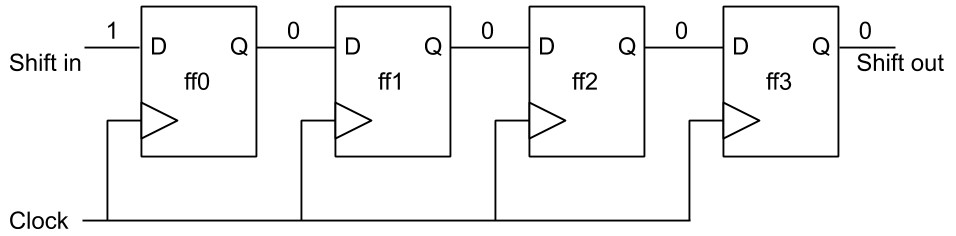

در ساده ترین شکل آن، یک لیست تغییر شامل تعدادی از عناصر ذخیره سازی (به عنوان مثال، فلیپ فلاپ) است که به صورت سری متصل هستند، به طوری که خروجی یک عنصر ذخیره سازی به ورودی بعدی وارد می شود. عناصر ذخیره سازی توسط سیگنال “ساعت مشترک” کنترل می شوند که به شرح زیر است.

مفاهیم اصلی ثبت شیفت

بیایید بگوییم که ما در حال استفاده از فلاپ های ارجاع شده به لبه مثبت هستیم.

تلنگرهایی را با علامت 0 و 1 در شکل 1 در نظر بگیرید (ff0 و ff1)، باید بدانید که ورودی ff0 ورودی ثبت Shift است.

ورودی ff1 خروجی ff0 است که مقدار فعلی آن نیز ff0 است.

در لبه ساعت مثبت، ff0 ورودی خود را ضبط می کند و ff1 مقدار فعلی ff0 را ضبط می کند.

اگر همه فلاپ ها شروع به تنظیم مجدد در 0 کنند و ما ورودی ثبت نام shift را در 1 نگه داریم، آن زمان یک لبه ساعت مثبت باعث می شود ff0 1 را ضبط کند.

در لبه ساعت مثبت دوم، ff1 عدد 1 را ضبط می کند زیرا نمونه خروجی ff0 را نمونه برداری کرده است.

تصویر شماره دو برای ثبت شیفت

در هر لبه ساعت متوالی مثبت، 1 به سمت تلنگر بعدی در زنجیره تغییر خواهد کرد تا وقتی که در خروجی ثبت شیفت ظاهر شود، یعنی خروجی ff3 در رجیستری شیفت 4 بیتی که در بالا نشان داده شده است، به نمایش گذاشته شود.

اگر در این مدت ورودی را در 1 نگه داشته باشیم، اکنون ریجستری همه 1 ها را در خود نگه می دارد که جز مراحلی برای ثبت شیفت خواهد بود.

کد ثبت شیفت در Verilog

Verilog یک زبان توصیفی سخت افزاری یا HDL است به این معنی که می توان از آن برای توصیف سخت افزار مدار منطقی واقعی استفاده کرد. به همین دلیل چندین جنبه از Verilog وجود دارد که با زبان های معمولی و رایج برنامه نویسی نرم افزار متفاوت است.

دو نکته مهم که باید هنگام نوشتن کد Verilog به خاطر بسپارید:

- دقیقا مانند یک مدار واقعی، بعضی از قسمت های کد Verilog به طور همزمان اجرا می شوند، نه به صورت متوالی و به صورت خط به خط نظیر یک برنامه نرم افزاری تک رشته ای

- همه سازه های Verilog نمی توانند سینتیسیز / synthesized شوند یا به یک مدار منطقی واقعی تبدیل شوند.

ما در این مثال قصد داریم تا کد نمونه را بنویسیم. با استفاده از این کار می توانید کدهای خود را در یک FPGA بارگیری کنید تا در واقع آن را در عمل مشاهده کنید و ببینید چه اتفاقی رخ می دهد.

اعلامیه ماژول / Module Declaration برای ثبت شیفت

برای ثبت شیفت در وریلوگ، در ابتدا برای شما با یک Module Declaration شروع خواهیم کرد.

module shiftReg4(

input shift_in,

input clock,

output shift_out

);

ماژول ها بلوک های اصلی ساختاری از طراحی مبتنی بر Verilog را تشکیل می دهند که منجر به ثبت شیفت خواهند شد.

با ثبت شیفت در ماژول، می توانیم نسخه های زیادی از آن را به دلخواه خود ایجاد كنیم و مشخص کنیم که چگونه در مدار قرار بگیرند.

وضعیت ورودی و خروجی اعلامیه های پورت هستند و آن ها تعیین می کنند چه موقع ثبت شیفت را تسریع می دهیم و چه اتصالی در دسترس خواهد بود.

در حال حاضر، ما فقط ورودی شیفت، ورودی ساعت و یک خروجی تغییر را داریم.

نمونه کامل ثبت شیفت در وریلوگ

Reg

در مرحله بعد، باید اتصالات مدار و سیمی را برای ثبت شیفت خود تعریف کنیم.

مانند نمودار فوق، ما از چهار فلیپ فلاپ برای این رجیستری تغییر 4 بیتی استفاده خواهیم کرد.

ما می توانیم با استفاده از کلمه کلیدی reg، یک flip flop ایجاد کنیم که به شرح زیر خواهد بود.

reg bit0;

reg bit1;

reg bit2;

reg bit3;

assign shift_out = bit3;

در اینجا چهار فلیپ فلاپی با نام bit0 از طریق bit3 داریم.

flipop flip1 خروجی خود را به درگاه shift_out متصل خواهد کرد و ما این کار را با یک عبارت اختصاصی انجام داده ایم که می تواند برای سیم کشی و منطق ترکیبی مورد استفاده قرار گیرد.

بلوک رویه ای / Procedural Block برای ثبت شیفت

حال باید به Verilog بگوییم که با این فلاپ ها چه کار کند و این در یک بلوک رویه ای و یا Procedural Block صورت خواهد گرفت.

یک بلوک رویه ای یا Procedural Block می تواند برای تعریف منطق ترکیبی یا پی در پی استفاده شود اما در این مثال، ما فقط از یک منطق پی در پی استفاده خواهیم کرد که به شرح زیر خواهد بود.

always @(posedge clock) begin

bit3 <= bit2;

bit2 <= bit1;

bit1 <= bit0;

bit0 <= shift_in;

end

endmodule

به یاد داشته باشید که بلوک رویه ای همیشه با کلمه کلیدی مختص به خود شروع می شود و به دنبال آن یک لیست حساس یا سنستیو ایجاد می شود. لیست حساسیت یا سنستیو به Verilog می گوید که چه زمان می تواند عبارات موجود در بلوک را ارزیابی کند.

وقتی این بلوک روی یک لبه ساعت مثبت فعال شود، ما به سادگی محتویات هر یک از تلنگرها را به فلاپ بعدی در زنجیره انتقال می دهیم.

بنابراین، bit3 آن چیزی را که قبلا در bit2 بود، به bit2 می دهد و آن را در bit1 و باقی بیت ها ذخیره می کند.

بلوک رویه ای در وریلوگ

Endmodule

شما می توانید با واژه endmodule، ماژول خود را به اتمام برسانید و در واقع ثبت شیفت را انجام داده باشید.

نمایه سازی و عملگر ثبت شیفت

ما در این جا کدی را برای Verilog ایجاد کرده ایم که مختص به مدار بوده است و با چهار فلاپ جداگانه به صورت سری متصل شده است.

reg [3:0] bits;

assign shift_out = bits[3];

always @(posedge clock) begin

bits <= bits << 1;

bits[0] <= shift_in;

end

یک علامت 4 بیتی را به طور هم زمان با نماد براکت “[3: 0]” مشخص کرده ایم که نشان می دهد که بیت 3 مهمترین بیت (MSB) است.

توجه داشته باشید که ما باید بیانیه اختصاصی خود را به سیم بیت 3 از ثبت به سیگنال shift_out خود تغییر دهیم.

اکنون، به جای نوشتن عبارت های بلوک رویه ای برای تغییر هر بیت به صورت جداگانه، می توانیم از یک عبارت واحد با عملگر سمت چپ shift (<<) استفاده کنیم تا آنچه را می خواهیم انجام دهیم.

با آرزوی موفقیت برای شما

با آرزوی موفقیت برای شما

در هر ساعت مثبت، داده های موجود در ریجستر 4 بیتی ما یک موقعیت به سمت چپ منتقل می شوند و MSB جدید در shift_out هدایت می شود.

همچنین توجه داشته باشید که این پیاده سازی تغییر جهت تغییر جهت را آسان می کند. در حال حاضر، ما از LSB به MSB در حال تغییر هستیم اما می توانیم به راحتی این کار را تغییر دهیم به طوری که از MSB به LSB تغییر می کند.

سنتز در Verilog / Synthesis in Verilog

نود و یا گره reg مقدار خود را نگه می دارد تا زمانی که مقدار دیگری به آن اختصاص داده شود.

هنگامی که کد برای ایجاد ساختارهای سخت افزاری واقعی ساخته می شود، بسته به نحوه اختصاص گره، این می تواند منجر به یک فلاپ شود.

سنتز در وریلوگ

استفاده / برنامه های کاربردی

رجیسترهای Shift اغلب در مواقعی که باید از داده های به داده های سریال منتقل داده شوند، کاربرد پیدا می کنند.

برای این منظور، ما به طور معمول یک سیگنال بار و سیم را به هر یک از ورودی های flip flop فرد در ثبت نام شیفت اضافه می کنیم تا داده های موازی بتوانند همه آنها را به یکباره در یک رجیستر shift بارگذاری کنند و سپس بیتی تغییر دهند.

برای پیاده سازی پروتکل های ارتباطی سریال مانند I2C و SPI، می توانیم از ماشین های استت و یا state machine استفاده کنیم تا هنگامی که بیت های داده های شخصی از رجیستری خارج می شوند، کنترل کنیم تا الزامات طرح مورد نظر خود را برآورده سازیم.

همچنین می توانیم سیم را به خروجی های هر فلیپ فلاپی اضافه کنیم تا یک دستگاه بتواند داده های سریال را به صورت بیت بیت دریافت کند و بعد از آنکه همه بیت ها تغییر کرده اند به طور موازی آن را از رجیستر shift بخوانیم.

سخن آخر

در این مقاله، ما در مورد چگونگی اجرای ثبت شیفت در Verilog صحبت کردیم و همچنین برای رویدادهای واقعی از مثال هایی همراه با کد استفاده کردیم که می توان در سخت افزارهای واقعی از آن استفاده کرد و نتیجه را مشاهده کرد.

امیدوارم این آموزش برای شما عزیزان مفید بوده باشد. درصورتیکه به تخصص FPGA علاقمند هستید و تمایل دارید ازین تخصص کسب درآمد کنید از آموزش FPGA آموزشگاه فنی پویان استفاده کنید.

برخی از دوره های در حال اجرا در آموزشگاه فنی پویان دوره های آموزش تعمیرات موبایل ، آموزش تعمیرات برد ، آموزش تعمیرات لوازم خانگی و … میباشند. برای اطلاع از تمامی دوره به صفحه اصلی سایت مراجعه کنید.

همچنین بخوانید:

بهبود عملکرد ایزولاسیون گالوانیک در سازه های نوری

درون کنسول بازی نینتندو چه چیزی قرار دارد؟